Tuesday, 12 May 2020

Wednesday, 26 February 2020

8 Bit Ripple Carry Addition Subtraction

8 Bit Ripple Carry Addition Subtraction

First we will make 1-bit full adder

/////Verilog code for 1-bit full adder

module full_adder(S, Cout, A, B, Cin);

output S, Cout;

input A, B, Cin;

wire w1,w2,w3;

xor(S,A,B,Cin);

and(w1,A,B);

and(w2,B,Cin);

and(w3,A,Cin);

or(Cout,w1,w2,w3);

endmodule

Now we will make 8-bit adder subtractor module

Note:

=>>> For addition put M=0

=>>> For subtraction put M=1

///// Verilog code for 8-bit adder subtractor

module adder_8(S, Cout, A, B, M);

output wire[7:0] S;

output wire Cout;

input wire [7:0] A, B;

input wire M;

wire [7:0] R;

wire w1,w2,w3,w4,w5,w6,w7;

xor (R[0],B[0],M);

xor (R[1],B[1],M);

xor (R[2],B[2],M);

xor (R[3],B[3],M);

xor (R[4],B[4],M);

xor (R[5],B[5],M);

xor (R[6],B[6],M);

xor (R[7],B[7],M);

full_adder FA1(S[0],w1,A[0],R[0],M);

full_adder FA2(S[1],w2,A[1],R[1],w1);

full_adder FA3(S[2],w3,A[2],R[2],w2);

full_adder FA4(S[3],w4,A[3],R[3],w3);

full_adder FA5(S[4],w5,A[4],R[4],w4);

full_adder FA6(S[5],w6,A[5],R[5],w5);

full_adder FA7(S[6],w7,A[6],R[6],w6);

full_adder FA8(S[7],Cout,A[7],R[7],w7);

endmodule

//// Test bench for 8-bit adder subtractor module

module add_sub_8bit_tb;

// Inputs

reg [7:0] A;

reg [7:0] B;

reg M;

// Outputs

wire [7:0] S;

wire Cout;

// Instantiate the Unit Under Test (UUT)

adder_8 uut (

.S(S),

.Cout(Cout),

.A(A),

.B(B),

.M(M)

);

initial begin

// Initialize Inputs

A = 01111011;

B = 01111000;

M = 0; //// M=0 for addition

#10

A = 11111011;

B = 11111000;

M = 1; //// M=1 subtraction

#10

A = 01000011;

B = 01101100;

M = 0; //// M=0 for addition

#10

A = 11000011;

B = 01111111;

M = 1; //// M=1 subtraction

// Wait 100 ns for global reset to finish

#10;

end

endmodule

////// Output

module adder_8(S, Cout, A, B, M);

output wire[7:0] S;

output wire Cout;

input wire [7:0] A, B;

input wire M;

wire [7:0] R;

wire w1,w2,w3,w4,w5,w6,w7;

xor (R[0],B[0],M);

xor (R[1],B[1],M);

xor (R[2],B[2],M);

xor (R[3],B[3],M);

xor (R[4],B[4],M);

xor (R[5],B[5],M);

xor (R[6],B[6],M);

xor (R[7],B[7],M);

full_adder FA1(S[0],w1,A[0],R[0],M);

full_adder FA2(S[1],w2,A[1],R[1],w1);

full_adder FA3(S[2],w3,A[2],R[2],w2);

full_adder FA4(S[3],w4,A[3],R[3],w3);

full_adder FA5(S[4],w5,A[4],R[4],w4);

full_adder FA6(S[5],w6,A[5],R[5],w5);

full_adder FA7(S[6],w7,A[6],R[6],w6);

full_adder FA8(S[7],Cout,A[7],R[7],w7);

endmodule

//// Test bench for 8-bit adder subtractor module

module add_sub_8bit_tb;

// Inputs

reg [7:0] A;

reg [7:0] B;

reg M;

// Outputs

wire [7:0] S;

wire Cout;

// Instantiate the Unit Under Test (UUT)

adder_8 uut (

.S(S),

.Cout(Cout),

.A(A),

.B(B),

.M(M)

);

initial begin

// Initialize Inputs

A = 01111011;

B = 01111000;

M = 0; //// M=0 for addition

#10

A = 11111011;

B = 11111000;

M = 1; //// M=1 subtraction

#10

A = 01000011;

B = 01101100;

M = 0; //// M=0 for addition

#10

A = 11000011;

B = 01111111;

M = 1; //// M=1 subtraction

// Wait 100 ns for global reset to finish

#10;

end

endmodule

////// Output

Tuesday, 25 February 2020

8 Bit Ripple Carry Adder (RCA) using Full Adder As Basic Cell

An adder is a digital circuit that performs addition

of numbers. In many computers and other kinds of processors adders are used in

the arithmetic logic units or ALU. They are also used in other parts of the

processor, where they are used to calculate addresses, table indices, increment

and decrement operators and similar operations.

Verilog Code for 1-bit full adder

module

full_adder(sum, cout, in1, in2, cin);

output wire sum;

output wire

cout;

input wire in1,

in2, cin;

wire temp1,

temp2, temp3;

xor(sum,in1,in2,cin);

and(temp1,in1,in2);

and(temp2,in1,cin);

and(temp3,in2,cin);

or(cout,temp1,temp2,temp3);

endmodule

Verilog code for 8-bit

RCA

module ripple_8(sum,cout,in1,in2,cin);

output wire[7:0] sum;

output wire cout;

input wire[7:0] in1,in2;

input wire cin;

wire c1,c2,c3,c4,c5,c6,c7;

full_adder FA1(sum[0],c1,in1[0],in2[0],cin);

full_adder FA2(sum[1],c2,in1[1],in2[1],c1);

full_adder FA3(sum[2],c3,in1[2],in2[2],c2);

full_adder FA4(sum[3],c4,in1[3],in2[3],c3);

full_adder FA5(sum[4],c5,in1[4],in2[4],c4);

full_adder FA6(sum[5],c6,in1[5],in2[5],c5);

full_adder FA7(sum[6],c7,in1[6],in2[6],c6);

full_adder FA8(sum[7],cout,in1[7],in2[7],c7);

endmodule

Test Bench for 8-bit ripple carry adder

module rca_tb;

// Inputs

reg [7:0] in1;

reg [7:0] in2;

reg cin;

// Outputs

wire [7:0] sum;

wire cout;

// Instantiate the Unit Under Test (UUT)

ripple_8 uut (

.sum(sum),

.cout(cout),

.in1(in1),

.in2(in2),

.cin(cin)

);

initial begin

// Initialize Inputs

in1 = 01111011;

in2 = 01111000;

cin = 0;

#10

in1 = 11111011;

in2 = 11111000;

cin = 0;

#10

in1 = 01000011;

in2 = 01101100;

cin = 0;

#10

in1 = 11000011;

in2 = 01111111;

cin = 0;

// Wait 10 ns for global reset to finish

#10;

end

endmodule

Note: Execute all the codes at the same time

///Output

Sunday, 16 February 2020

Verilog code for full adder

Full Adder

A full adder adds binary numbers and accounts for values

carried in as well as out. A one-bit full-adder adds three one-bit numbers,

often written as A, B, and Cin; A and B are the operands, and Cin is a bit

carried in from the previous less-significant stage.The full adder is usually a

component in a cascade of adders, which add 8, 16, 32, etc. bit binary numbers.

The circuit produces a two-bit output. Output carry and sum typically represented

by the signals Cout and S, where the sum equals

2Cout + S.

A full adder can be implemented in many different ways such

as with a custom transistor-level circuit or composed of other gates. One

example implementation is with

S = A ⊕

B ⊕

Cin and Cout = (A ⋅ B) + (Cin ⋅ (A ⊕ B))

A

|

B

|

Cin

|

S

|

Cout

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

S = A ⊕ B ⊕ Cin

Cout = (A ⋅ B) + (Cin ⋅

(A ⊕ B))

///Verilog code for full adder

module full_adder(sum, cout, in1, in2, cin);

output wire sum;

output wire cout;

input wire in1, in2, cin;

wire temp1, temp2, temp3;

xor(sum,in1,in2,cin);

and(temp1,in1,in2);

and(temp2,in1,cin);

and(temp3,in2,cin);

or(cout,temp1,temp2,temp3);

endmodule

output wire sum;

output wire cout;

input wire in1, in2, cin;

wire temp1, temp2, temp3;

xor(sum,in1,in2,cin);

and(temp1,in1,in2);

and(temp2,in1,cin);

and(temp3,in2,cin);

or(cout,temp1,temp2,temp3);

endmodule

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

Output of full adder

Output of full adder

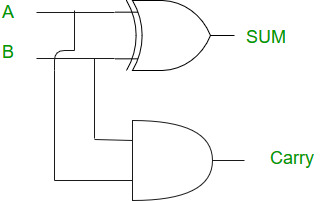

Verilog Code for Half Adder

Verilog Code for Half Adder

An adder is a digital circuit that performs addition of

numbers. The half adder adds two binary digits called as augend and addend and

produces two outputs as sum and carry; XOR is applied to both inputs to produce

sum and AND gate is applied to both inputs to produce carry.

A

|

B

|

SUM

|

Carry

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

//Verilog code for half adder

Module Half_adder(SUM, Carry, A, B);

output SUM;

output Carry;

input A, B;

xor(SUM, A, B);

and(Carry, A, B);

endmodule;

Subscribe to:

Comments (Atom)