Full Adder

A full adder adds binary numbers and accounts for values

carried in as well as out. A one-bit full-adder adds three one-bit numbers,

often written as A, B, and Cin; A and B are the operands, and Cin is a bit

carried in from the previous less-significant stage.The full adder is usually a

component in a cascade of adders, which add 8, 16, 32, etc. bit binary numbers.

The circuit produces a two-bit output. Output carry and sum typically represented

by the signals Cout and S, where the sum equals

2Cout + S.

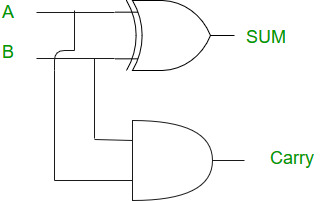

A full adder can be implemented in many different ways such

as with a custom transistor-level circuit or composed of other gates. One

example implementation is with

S = A ⊕

B ⊕

Cin and Cout = (A ⋅ B) + (Cin ⋅ (A ⊕ B))

A

|

B

|

Cin

|

S

|

Cout

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

S = A ⊕ B ⊕ Cin

Cout = (A ⋅ B) + (Cin ⋅

(A ⊕ B))

///Verilog code for full adder

module full_adder(sum, cout, in1, in2, cin);

output wire sum;

output wire cout;

input wire in1, in2, cin;

wire temp1, temp2, temp3;

xor(sum,in1,in2,cin);

and(temp1,in1,in2);

and(temp2,in1,cin);

and(temp3,in2,cin);

or(cout,temp1,temp2,temp3);

endmodule

output wire sum;

output wire cout;

input wire in1, in2, cin;

wire temp1, temp2, temp3;

xor(sum,in1,in2,cin);

and(temp1,in1,in2);

and(temp2,in1,cin);

and(temp3,in2,cin);

or(cout,temp1,temp2,temp3);

endmodule

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

Output of full adder

Output of full adder