Verilog Code for Half Adder

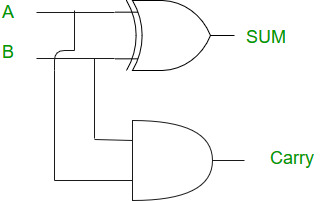

An adder is a digital circuit that performs addition of

numbers. The half adder adds two binary digits called as augend and addend and

produces two outputs as sum and carry; XOR is applied to both inputs to produce

sum and AND gate is applied to both inputs to produce carry.

A

|

B

|

SUM

|

Carry

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

//Verilog code for half adder

Module Half_adder(SUM, Carry, A, B);

output SUM;

output Carry;

input A, B;

xor(SUM, A, B);

and(Carry, A, B);

endmodule;

No comments:

Post a Comment