8 Bit Ripple Carry Addition Subtraction

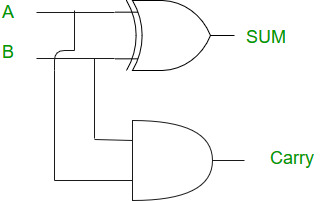

First we will make 1-bit full adder

/////Verilog code for 1-bit full adder

module full_adder(S, Cout, A, B, Cin);

output S, Cout;

input A, B, Cin;

wire w1,w2,w3;

xor(S,A,B,Cin);

and(w1,A,B);

and(w2,B,Cin);

and(w3,A,Cin);

or(Cout,w1,w2,w3);

endmodule

Now we will make 8-bit adder subtractor module

Note:

=>>> For addition put M=0

=>>> For subtraction put M=1

///// Verilog code for 8-bit adder subtractor

module adder_8(S, Cout, A, B, M);

output wire[7:0] S;

output wire Cout;

input wire [7:0] A, B;

input wire M;

wire [7:0] R;

wire w1,w2,w3,w4,w5,w6,w7;

xor (R[0],B[0],M);

xor (R[1],B[1],M);

xor (R[2],B[2],M);

xor (R[3],B[3],M);

xor (R[4],B[4],M);

xor (R[5],B[5],M);

xor (R[6],B[6],M);

xor (R[7],B[7],M);

full_adder FA1(S[0],w1,A[0],R[0],M);

full_adder FA2(S[1],w2,A[1],R[1],w1);

full_adder FA3(S[2],w3,A[2],R[2],w2);

full_adder FA4(S[3],w4,A[3],R[3],w3);

full_adder FA5(S[4],w5,A[4],R[4],w4);

full_adder FA6(S[5],w6,A[5],R[5],w5);

full_adder FA7(S[6],w7,A[6],R[6],w6);

full_adder FA8(S[7],Cout,A[7],R[7],w7);

endmodule

//// Test bench for 8-bit adder subtractor module

module add_sub_8bit_tb;

// Inputs

reg [7:0] A;

reg [7:0] B;

reg M;

// Outputs

wire [7:0] S;

wire Cout;

// Instantiate the Unit Under Test (UUT)

adder_8 uut (

.S(S),

.Cout(Cout),

.A(A),

.B(B),

.M(M)

);

initial begin

// Initialize Inputs

A = 01111011;

B = 01111000;

M = 0; //// M=0 for addition

#10

A = 11111011;

B = 11111000;

M = 1; //// M=1 subtraction

#10

A = 01000011;

B = 01101100;

M = 0; //// M=0 for addition

#10

A = 11000011;

B = 01111111;

M = 1; //// M=1 subtraction

// Wait 100 ns for global reset to finish

#10;

end

endmodule

////// Output

module adder_8(S, Cout, A, B, M);

output wire[7:0] S;

output wire Cout;

input wire [7:0] A, B;

input wire M;

wire [7:0] R;

wire w1,w2,w3,w4,w5,w6,w7;

xor (R[0],B[0],M);

xor (R[1],B[1],M);

xor (R[2],B[2],M);

xor (R[3],B[3],M);

xor (R[4],B[4],M);

xor (R[5],B[5],M);

xor (R[6],B[6],M);

xor (R[7],B[7],M);

full_adder FA1(S[0],w1,A[0],R[0],M);

full_adder FA2(S[1],w2,A[1],R[1],w1);

full_adder FA3(S[2],w3,A[2],R[2],w2);

full_adder FA4(S[3],w4,A[3],R[3],w3);

full_adder FA5(S[4],w5,A[4],R[4],w4);

full_adder FA6(S[5],w6,A[5],R[5],w5);

full_adder FA7(S[6],w7,A[6],R[6],w6);

full_adder FA8(S[7],Cout,A[7],R[7],w7);

endmodule

//// Test bench for 8-bit adder subtractor module

module add_sub_8bit_tb;

// Inputs

reg [7:0] A;

reg [7:0] B;

reg M;

// Outputs

wire [7:0] S;

wire Cout;

// Instantiate the Unit Under Test (UUT)

adder_8 uut (

.S(S),

.Cout(Cout),

.A(A),

.B(B),

.M(M)

);

initial begin

// Initialize Inputs

A = 01111011;

B = 01111000;

M = 0; //// M=0 for addition

#10

A = 11111011;

B = 11111000;

M = 1; //// M=1 subtraction

#10

A = 01000011;

B = 01101100;

M = 0; //// M=0 for addition

#10

A = 11000011;

B = 01111111;

M = 1; //// M=1 subtraction

// Wait 100 ns for global reset to finish

#10;

end

endmodule

////// Output